## FTK to Level-2 Interface Card

# **User's Guide**

-- PIRIELJIMUNAIRY --

December 15, 2016

Version 2.4

Originators: John T. Anderson, Michael Oberling

## **Table of Contents**

| 1 G                 | ENERAL INFORMATION                                 |     |

|---------------------|----------------------------------------------------|-----|

| 1.1                 | ATCA shelf implementation                          | . 1 |

| 1.2                 | Front Panel                                        | . 1 |

| 1.3                 | Board Layout Overview                              | . 2 |

| 1.4                 | Power Distribution                                 | 3   |

| 1.5                 | Control Architecture                               | -   |

| 1.6                 | System Monitoring                                  |     |

| 1.6.1               |                                                    |     |

| 1.6.2               |                                                    |     |

| 2 E                 | LECTRICAL & MECHANICAL SPECIFICATIONS              |     |

| 2.1                 | PC board construction                              |     |

| 2.2                 | Mechanical specifics                               |     |

| 2.3                 | Power and Cooling requirements                     |     |

| 2.4                 | Front Panel Connectors                             |     |

| 2.4.1               |                                                    |     |

| 2.4.2               |                                                    |     |

| 2.4.3               |                                                    |     |

| 2.4.4               |                                                    |     |

| 2.4.5               |                                                    |     |

| 2.5                 | Rear Connectors                                    |     |

| 2.6                 | Physical Interface to ATCA backplane               |     |

| -                   | UNCTIONAL OVERVIEW                                 |     |

| 3.1                 | Basic Features                                     |     |

| 3.2                 | Block Diagram                                      |     |

| 3.2.1               | , , , , , , , , , , , , , , , , , , , ,            |     |

| 3.3                 | Clock Domains within the FLIC                      |     |

| 3.4                 | DDR Memory Buffers                                 |     |

| 3.5                 | Data Processing Pipeline Overview                  |     |

| 3.6                 | ATCA Interface Overview                            |     |

| 3.6.1<br><b>3.7</b> |                                                    |     |

| 3.7<br>3.8          | Flow Control<br>Secondary Parallel Mesh            |     |

|                     | ONTROLLING THE FLIC                                |     |

|                     | UDP Slow Control Packet Structure                  |     |

| <b>4.1</b><br>4.1.1 |                                                    |     |

| 4.1.1               |                                                    |     |

| 4.1.2               |                                                    |     |

| 4.1.3               |                                                    |     |

| 4.1.4<br>4.2        | Slow Control Commands                              |     |

| 4.2                 | Physical Interface between PIC and Management FPGA |     |

| 4.4                 | Secondary methods of slow control                  |     |

| 4.4.1               | -                                                  |     |

| 4.4.2               |                                                    |     |

| 4.4.3               |                                                    |     |

| -                   | ATA PROCESSING PIPELINE FIRMWARE                   |     |

| 5 D                 | Serial interface to/from the SSB                   |     |

| 5.1.1               |                                                    |     |

| 5.1.2               | ·                                                  |     |

| -                   | 1.2.1 Power-on handshaking                         |     |

|                     | 0                                                  |     |

| 5.1.3                                                                                                                                                                                                                                                                                                       | PRBS test mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 5.2                                                                                                                                                                                                                                                                                                         | FIFO Buffers in the pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31                                           |

| 5.3                                                                                                                                                                                                                                                                                                         | The Core Crate Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32                                           |

| 5.3.1                                                                                                                                                                                                                                                                                                       | Initial Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33                                           |

| 5.3.2                                                                                                                                                                                                                                                                                                       | Error Detection in the Core Crate Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33                                           |

| 5.3.3                                                                                                                                                                                                                                                                                                       | Processing the Record Header                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34                                           |

| 5.3.4                                                                                                                                                                                                                                                                                                       | Processing Track Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34                                           |

| 5.3.5                                                                                                                                                                                                                                                                                                       | Processing Record Trailers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 36                                           |

| 5.3.6                                                                                                                                                                                                                                                                                                       | 6 "Manufactured" Record Trailers in response to errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 37                                           |

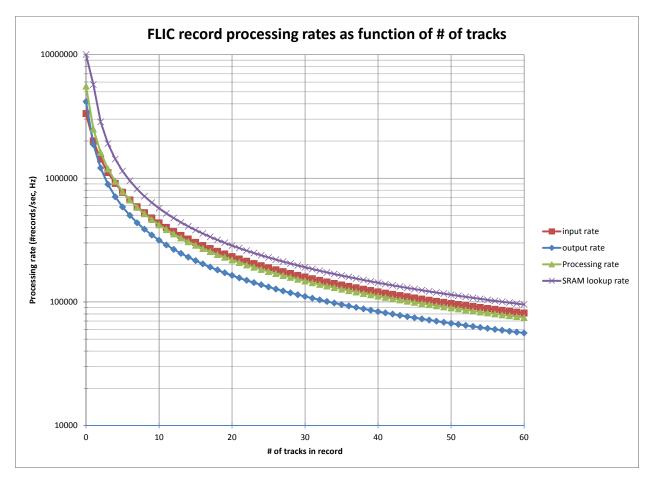

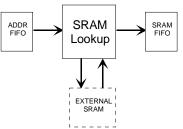

| 5.4                                                                                                                                                                                                                                                                                                         | SRAM Lookup Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 37                                           |

| 5.4.1                                                                                                                                                                                                                                                                                                       | Timing Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 38                                           |

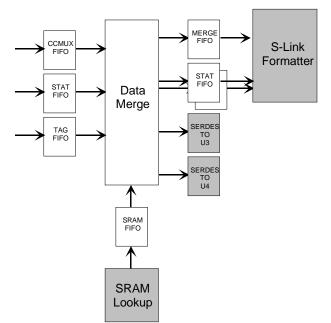

| 5.5                                                                                                                                                                                                                                                                                                         | Data Merge Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38                                           |

| 5.5.1                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                              |

| 5.5                                                                                                                                                                                                                                                                                                         | 5.1.1 Merge process for Pixel layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40                                           |

| 5.5                                                                                                                                                                                                                                                                                                         | 5.1.2 Merge operation for Silicon layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 41                                           |

| 5.5.2                                                                                                                                                                                                                                                                                                       | Merging of the Record Trailer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 41                                           |

| 5.5.3                                                                                                                                                                                                                                                                                                       | Error accumulation and forwarding in the Merge machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 42                                           |

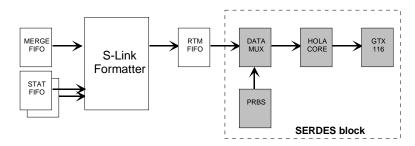

| 5.6                                                                                                                                                                                                                                                                                                         | S-Link Formatter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 42                                           |

| 5.6.1                                                                                                                                                                                                                                                                                                       | . Error masking and the S-Link footer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43                                           |

| 5.0                                                                                                                                                                                                                                                                                                         | 6.1.1 S-Link footer for records with no error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                              |

| 5.0                                                                                                                                                                                                                                                                                                         | 6.1.2 Added data and S-Link footer for records with error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 44                                           |

| 5.0                                                                                                                                                                                                                                                                                                         | 6.1.3 Special S-Link Footer generated upon failure of status collection subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 44                                           |

| 5.7                                                                                                                                                                                                                                                                                                         | Implementation of CERN S-Link (HOLA) core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |

| 5.8                                                                                                                                                                                                                                                                                                         | Flow Control in the processing pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45                                           |

|                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                              |

| 5.9                                                                                                                                                                                                                                                                                                         | Event Selection Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 46                                           |

| <b>5.9</b><br>5.9.1                                                                                                                                                                                                                                                                                         | Event Selection Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                              |

|                                                                                                                                                                                                                                                                                                             | Event Selection Methodology<br>Tag FIFO Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46                                           |

| 5.9.1                                                                                                                                                                                                                                                                                                       | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 46<br>46                                     |

| 5.9.1<br>5.9.2<br>5.9.3                                                                                                                                                                                                                                                                                     | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 46<br>46<br>47                               |

| 5.9.1<br>5.9.2<br>5.9.3                                                                                                                                                                                                                                                                                     | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 46<br>46<br>47<br><b>48</b>                  |

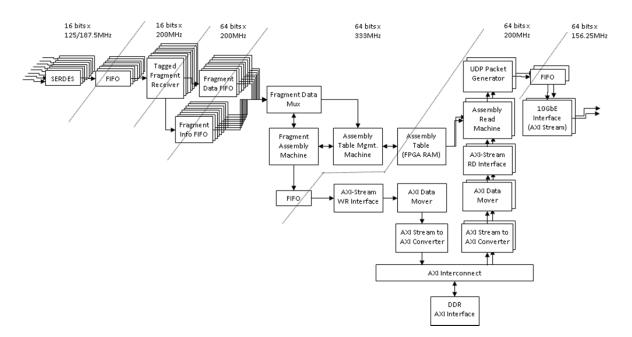

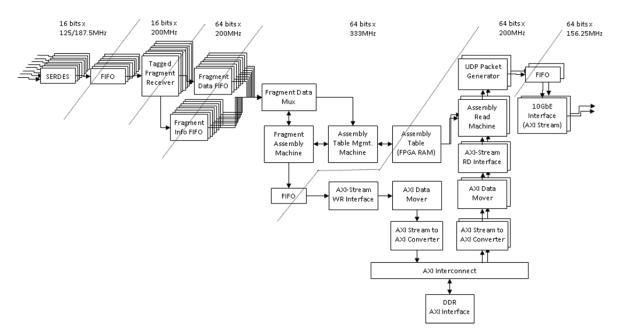

| 5.9.1<br>5.9.2<br>5.9.3<br>6 A                                                                                                                                                                                                                                                                              | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs         TCA INTERFACE FIRMWARE         Inter-FPGA SERDES Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46<br>46<br>47<br>48<br>49                   |

| 5.9.1<br>5.9.2<br>5.9.3<br>6 A'<br>6.1                                                                                                                                                                                                                                                                      | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs         TCA INTERFACE FIRMWARE         Inter-FPGA SERDES Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46<br>46<br>47<br>48<br>49<br>49             |

| 5.9.1<br>5.9.2<br>5.9.3<br><b>6 A'</b><br><b>6.1</b><br>6.1.1                                                                                                                                                                                                                                               | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs         TCA INTERFACE FIRMWARE         Inter-FPGA SERDES Transceiver         FIFOs         Tagged Record Reception Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46<br>46<br>47<br>49<br>49<br>50             |

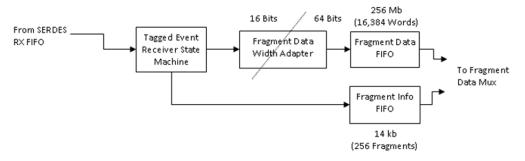

| 5.9.1<br>5.9.2<br>5.9.3<br>6 A'<br>6.1<br>6.1.1<br>6.2                                                                                                                                                                                                                                                      | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs         TCA INTERFACE FIRMWARE         Inter-FPGA SERDES Transceiver         FIFOs         Tagged Record Reception Logic         Tagged Record Receiver State Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46<br>46<br>47<br>48<br>49<br>50<br>50       |

| 5.9.1<br>5.9.2<br>5.9.3<br>6 A'<br>6.1<br>6.1.1<br>6.2<br>6.2.1                                                                                                                                                                                                                                             | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs         TCA INTERFACE FIRMWARE         Inter-FPGA SERDES Transceiver         FIFOs         Tagged Record Reception Logic         Tagged Record Receiver State Machine         Fragment Info FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |

| 5.9.1<br>5.9.2<br>5.9.3<br>6 A'<br>6.1<br>6.2<br>6.2.1<br>6.2.2                                                                                                                                                                                                                                             | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs         TCA INTERFACE FIRMWARE         Inter-FPGA SERDES Transceiver         FIFOs         Tagged Record Reception Logic         Tagged Record Receiver State Machine         Fragment Info FIFO         Fragment Data Width Adapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46<br>47<br>48<br>49<br>49<br>50<br>51<br>51 |

| 5.9.1<br>5.9.2<br>5.9.3<br>6 A'<br>6.1<br>6.1.1<br>6.2.1<br>6.2.1<br>6.2.2<br>6.2.3                                                                                                                                                                                                                         | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs         TCA INTERFACE FIRMWARE         Inter-FPGA SERDES Transceiver         FIFOs         Tagged Record Reception Logic         Tagged Record Receiver State Machine         Fragment Info FIFO         Fragment Data Width Adapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46<br>47<br>48<br>49<br>49<br>50<br>51<br>51 |

| 5.9.1<br>5.9.2<br>5.9.3<br>6 A'<br>6.1<br>6.1.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                                                                                                                                                                                                                  | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs         TCA INTERFACE FIRMWARE         Inter-FPGA SERDES Transceiver         FIFOs         Tagged Record Reception Logic         Tagged Record Receiver State Machine         Fragment Info FIFO         Fragment Data Width Adapter         Fragment Data FIFO         Fragment Assembly                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                              |

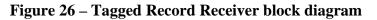

| 5.9.1<br>5.9.2<br>5.9.3<br>6 A'<br>6.1<br>6.1.1<br>6.2<br>6.2.1<br>6.2.3<br>6.2.4<br>6.3                                                                                                                                                                                                                    | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs         TCA INTERFACE FIRMWARE         Inter-FPGA SERDES Transceiver         FIFOs         Tagged Record Reception Logic         Tagged Record Receiver State Machine         Fragment Info FIFO         Fragment Data Width Adapter         Fragment Data FIFO         Fragment Data Multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |

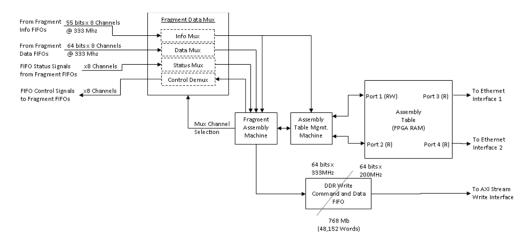

| 5.9.1<br>5.9.2<br>5.9.3<br><b>6 A'</b><br><b>6.1</b><br><b>6.1</b><br><b>6.2</b><br><b>6.2.1</b><br><b>6.2.3</b><br><b>6.2.4</b><br><b>6.3</b><br><b>6.3.1</b>                                                                                                                                              | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs         TCA INTERFACE FIRMWARE         Inter-FPGA SERDES Transceiver         FIFOs         Tagged Record Reception Logic         Tagged Record Receiver State Machine         Fragment Info FIFO         Fragment Data Width Adapter         Fragment Data FIFO         Fragment Assembly         Fragment Data Multiplexer         Fragment Assembly State Machine                                                                                                                                                                                                                                                                                                                                                                                                 |                                              |

| 5.9.1<br>5.9.2<br>5.9.3<br><b>6 A</b> '<br><b>6.1</b><br><b>6.1.1</b><br><b>6.2</b><br><b>6.2.1</b><br><b>6.2.2</b><br><b>6.2.3</b><br><b>6.2.4</b><br><b>6.3</b><br><b>6.3.1</b><br><b>6.3.2</b>                                                                                                           | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs         TCA INTERFACE FIRMWARE         Inter-FPGA SERDES Transceiver         FIFOs         Tagged Record Reception Logic         Tagged Record Receiver State Machine         Fragment Info FIFO         Fragment Data Width Adapter         Fragment Data FIFO         Fragment Data Multiplexer         Fragment Assembly         State Machine         Fragment Data Multiplexer         Assembly Table                                                                                                                                                                                                                                                                                                                                                          |                                              |

| 5.9.1<br>5.9.2<br>5.9.3<br><b>6</b> A'<br>6.1<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br><b>6.3</b><br>6.3.1<br>6.3.2<br>6.3.3                                                                                                                                                                                  | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs         TCA INTERFACE FIRMWARE         Inter-FPGA SERDES Transceiver         FIFOs         Tagged Record Reception Logic         Tagged Record Receiver State Machine         Fragment Info FIFO         Fragment Data Width Adapter         Fragment Data FIFO         Fragment Assembly         Fragment Assembly State Machine         Assembly Table                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |

| 5.9.1<br>5.9.2<br>5.9.3<br>6 A'<br>6.1<br>6.1.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4                                                                                                                                                                              | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs         TCA INTERFACE FIRMWARE         Inter-FPGA SERDES Transceiver         FIFOs         Tagged Record Reception Logic         Tagged Record Receiver State Machine         Fragment Info FIFO         Fragment Data Width Adapter         Fragment Data FIFO         Fragment Assembly         Fragment Assembly         Fragment Assembly State Machine         Assembly Table         Fragment Data Table Management State Machine         Format of the data assembly         Details of the assembly header                                                                                                                                                                                                                                                  |                                              |

| 5.9.1<br>5.9.2<br>5.9.3<br>6 A'<br>6.1<br>6.1.1<br>6.2<br>6.2.3<br>6.2.4<br>6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.4<br>6.4                                                                                                                                                                         | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs         TCA INTERFACE FIRMWARE         Inter-FPGA SERDES Transceiver         FIFOs         Tagged Record Reception Logic         Tagged Record Receiver State Machine         Fragment Info FIFO         Fragment Data Width Adapter         Fragment Data FIFO         Fragment Data BIFO         Fragment Data BIFO         Fragment Data BIFO         Fragment Data TIFO         Fragment Data State Machine         Assembly         State Machine         Assembly Table         Fragment Data Table Management State Machine         Format of the data assembly |                                              |

| 5.9.1<br>5.9.2<br>5.9.3<br><b>6 A</b> '<br><b>6.1</b><br><b>6.2</b><br><b>6.2.1</b><br><b>6.2.1</b><br><b>6.2.2</b><br><b>6.2.3</b><br><b>6.2.4</b><br><b>6.3</b><br><b>6.3.1</b><br><b>6.3.2</b><br><b>6.3.1</b><br><b>6.3.2</b><br><b>6.3.3</b><br><b>6.3.4</b><br><b>6.4</b><br><b>6.5</b><br><b>6.6</b> | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs         TCA INTERFACE FIRMWARE         Inter-FPGA SERDES Transceiver         FIFOs         Tagged Record Reception Logic         Tagged Record Receiver State Machine         Fragment Info FIFO         Fragment Data Width Adapter         Fragment Data FIFO         Fragment Data FIFO         Fragment Data Multiplexer         Fragment Assembly         Fragment Assembly State Machine         Assembly Table         Fragment Data Multiplexer         Fragment Assembly State Machine         Assembly Table         Fragment Data Table Management State Machine         Format of the data assembly.         Details of the assembly header         AXI Based Interconnect         UDP Packet Generator                                                 |                                              |

| 5.9.1<br>5.9.2<br>5.9.3<br><b>6 A</b> '<br><b>6.1</b><br><b>6.2</b><br><b>6.2.1</b><br><b>6.2.1</b><br><b>6.2.2</b><br><b>6.2.3</b><br><b>6.2.4</b><br><b>6.3</b><br><b>6.3.1</b><br><b>6.3.2</b><br><b>6.3.1</b><br><b>6.3.2</b><br><b>6.3.3</b><br><b>6.3.4</b><br><b>6.4</b><br><b>6.5</b><br><b>6.6</b> | Event Selection Methodology         Tag FIFO Usage         Data Transfer between FPGAs         Pipeline-level selection control in ATCA Interface FPGAs         TCA INTERFACE FIRMWARE         Inter-FPGA SERDES Transceiver         FIFOs         Tagged Record Reception Logic         Tagged Record Receiver State Machine         Fragment Info FIFO         Fragment Data Width Adapter         Fragment Data FIFO         Fragment Data Kultiplexer         Fragment Data Multiplexer         Fragment Assembly         Fragment Data Multiplexer         Fragment Data Multiplexer         Fragment Data Sembly State Machine         Fragment Data Table Management State Machine         Format of the data assembly         Details of the assembly header                                                                                                                                                        |                                              |

## **1 GENERAL INFORMATION**

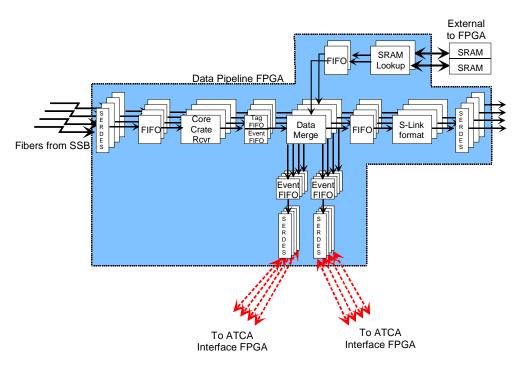

The FTK to Level-2 Interface Card (FLIC) is an Advanced Telecommunications Computing Architecture (ATCA) module designed as part of the ATLAS Fast TracKer (FTK) to receive data records from Second Stage Boards (SSBs) via optical fiber, decode the packet structure of those records, perform on-the-fly lookup of detector physical geometry information from local RAM buffers, merge the physical geometry data into the SSB tracks, package the merged data into S-Link packets and transmit them to the ReadOut Subsystem (ROS) using SFP optical transceivers on a rear transition module. Each FLIC has eight front-panel SFP fiber optic inputs, one for each of eight "half-SSB" boards, such that two FLICs collect all the data from the FTK system. Each FLIC implements DDR ram buffers and four 10GbE links so that selected records of interest may be copied to ATCA processor blades resident in the same ATCA shelf as the FLIC. A mesh of internal FPGA-to-FPGA serial links allow collection of data from all "half-SSBs" into a single assembled record fragment for transmission to a processor blade over any of the four 10GbE links.

The system specification document for the FLIC defines the specifications of the module. This document contains specific information regarding details of the hardware and firmware design to assist the reader in the use of the module. Statements herein are intended to convey *how* the design achieves the specifications as stated, *not* the specifications themselves. This revision of the document applies only to the **production** FLIC boards. An earlier version of this document provides information about the prototypes.

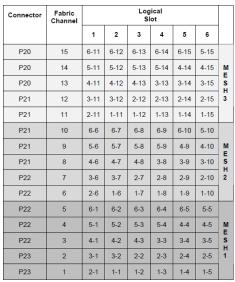

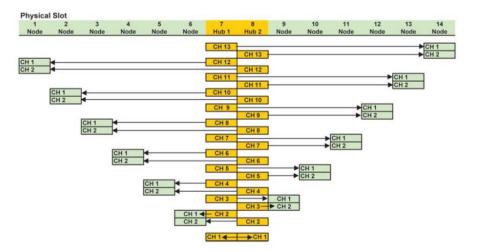

## 1.1 ATCA shelf implementation

The ATCA shelf used for the FLIC system contains 6 slots, connected together by a 3x mesh backplane. Two FLIC boards are installed into hub slots 1 and 2. This allows each FLIC, which uses only one mesh of the 3X fabric, to have a private ATCA channel to each of slots 3, 4, 5 and 6. It is envisioned that these slots of the ATCA shelf will be populated by processor boards to enable monitoring of the data flowing through each FLIC.

The FLIC implements a DIMM socket intended to house an Intelligent Platform Management Controller (IPMC) module designed by the Laboratoire d'Annecy-le-Vieux de Physique des Particules (LAPP) for the ATLAS collaboration. This IPMC implements all communication with the Shelf Manager and is the only part of the FLIC that connects to the Base Interface of the ATCA shelf.

## **1.2 Front Panel**

**Figure 1 – Front panel of FLIC**

The front panel of the FLIC is shown in Figure 1. All LEDs are grouped together in one place left of the SFPs. In the middle, eight SFP optical modulators provide connections to the rest of FTK. To the right of the SFPs, is the Ethernet cable connection that provides a direct interface to the FLIC's

microprocessor for test bench operation. At the far right, is the RJ-11 connector used to program the onboard microprocessor.

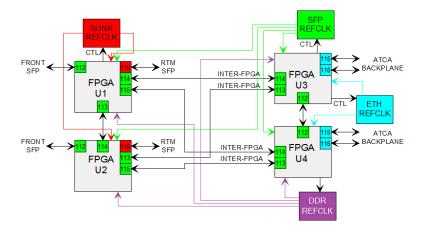

## 1.3 Board Layout Overview

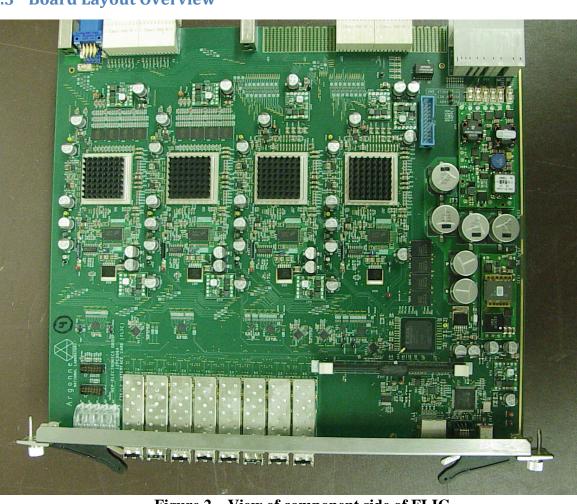

**Figure 2** – View of component side of **FLIC**

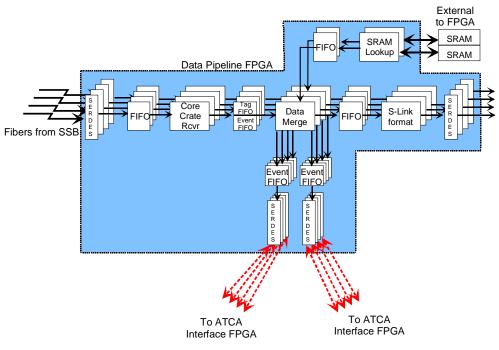

Figure 2 shows the component side of the board. The FLIC holds five FPGAs; four Virtex-6 main FPGAs are easily identified by the large heatsinks. These are commonly referred to as "U1" through "U4", respectively from left to right. "U1" and "U2" are connected to the eight SFP optical modulators at the front of the module and also connect to eight more SFPs through the rear transition module (RTM) connector. "U3" and "U4" connect to "U1" and "U2" via an internal mesh of high speed serial links and also connect to four 10GbE channels of the ATCA main fabric.

At the lower right of Figure 2, near the power supply, a smaller Spartan-3 FPGA may be seen; this is referred to as the "Management FPGA". A Microchip PIC microcontroller is also located in this corner of the board that interfaces to the front panel Ethernet connector and the Management FPGA to provide register access and slow control. The large DIMM socket at lower right is for the LAPP IPMC module that connects to the ATCA Shelf Manager, the Management FPGA and the PIC micro.

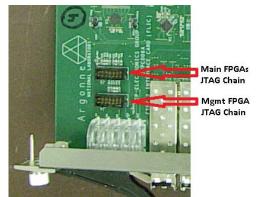

JTAG connections for the FPGAs and LED light pipes are seen at bottom right. Two JTAG connectors are used to separate the Management FPGA and the main FPGA chains by voltage. A blue debug/programming connector for the IPMC module is located near the ATCA P1 connector.

## **1.4 Power Distribution**

48V power from the ATCA backplane enters via connector P1 through a PIM300 power entry module in accordance with ATCA specifications. A PTEA420033N2AD 48V to 3.3V, 20A converter provides bulk power to the board. Test points on the board allow connection of a benchtop 48V supply to ease diagnosis & repair of the hardware. This bulk converter is enabled by processor control. Only the PIC microcontroller, the Spartan-3 FPGA and the IPMC interface module are powered from ATCA management power. Each of the four main FPGAs have point-of-load power converters to derive required FPGA and DDR memory voltages from the board-wide +3.3V, once the bulk converter is enabled. When the IPMC interface module is installed, the power on/power off commands sent by the Shelf Manager are decoded by the IPMC and passed through the on-board PIC microcontroller to the power modules.

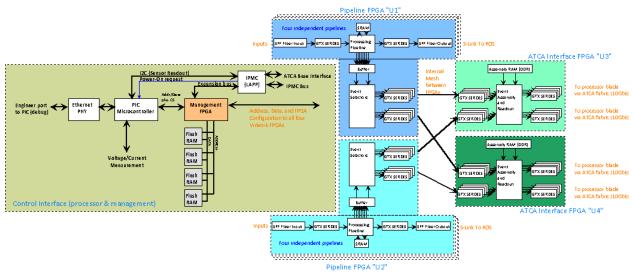

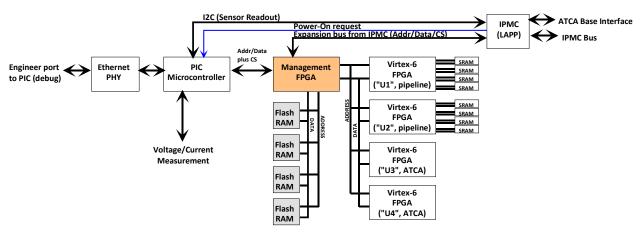

## 1.5 Control Architecture

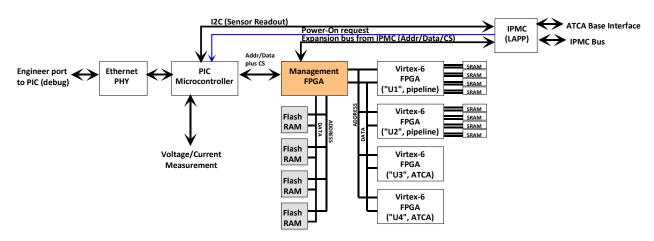

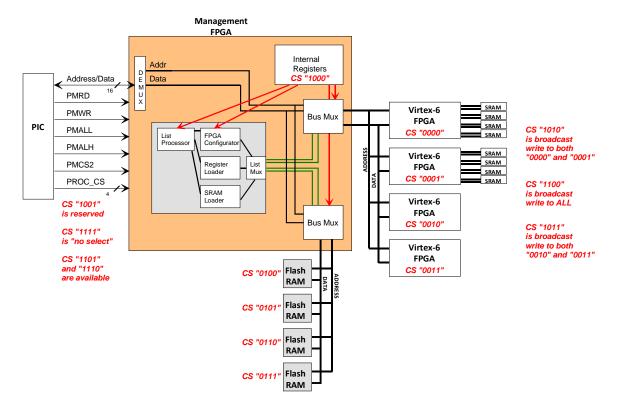

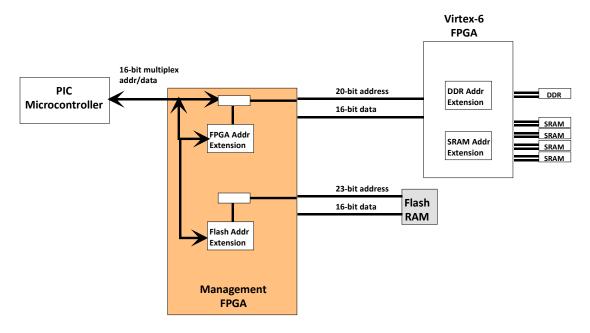

The PIC microcontroller is connected to a front panel Ethernet port, and communicates with a small Spartan-3 FPGA. The Spartan-3 implements a parallel address bus and a parallel data bus connected to each of the four main FPGAs for slow control purposes, as shown in Figure 3. The PIC performs register read or write operations in response to simple UDP commands packets with a target device number to select between FPGAs. This is described in detail in Section 4.1.

**Figure 3 – slow control architecture of FLIC**

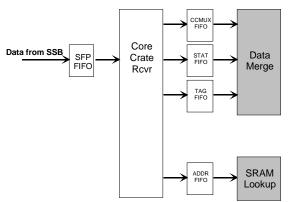

Firmware images for the main FPGAs are stored in local non-volatile Flash memory, managed by the Spartan-3 Management FPGA that may be loaded through the front panel Ethernet port. Each Flash memory chip is partitioned into areas to contain a main FPGA firmware image and module ID coordinate data storage for transfer to the SRAMs of the two Pipeline FPGAs. After the main board power is enabled, state machines in the Management FPGA are used to load the main FPGAs from the Flash memory. After FPGA initialization a separate command initiates automated transfer of the module ID data from the Flash memories into the SRAM module ID lookup tables associated with FPGAs U1 and

U2. After all initialization of FPGAs and memories is complete, operational setup is achieved by writing individual registers of the FPGAs. The 35-bit expansion bus of the LAPP IPMC module has been connected to the Spartan-3 to allow for future development of firmware to support slow control and firmware maintenance through the IPMC module.

## 1.6 System Monitoring

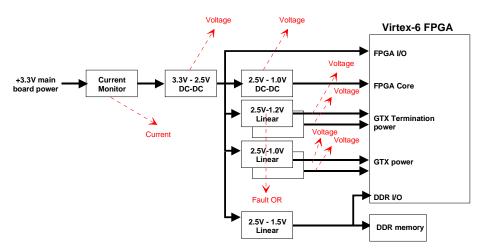

Analog multiplexers allow the PIC microcontroller to measure all voltages associated with each main FPGA using the A/D converter of the PIC. The point-of-load power distribution sub-system for each Virtex-6 FPGA is shown in Figure 4.

**Figure 4 – Point of load distribution and monitoring**

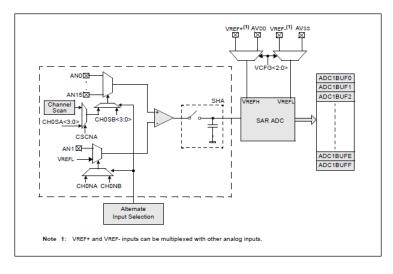

Eight analog data values are available per main FPGA; six voltages, one current and one fault signal. The 'fault' signal is tied by a resistive divider to the +3.3V and reads a known fraction of +3.3V if no fault is present, 0V if any of the GTX linear regulators are in a fault state. The PIC32MX695F512L implements a 16-channel, 10-bit multiplexed ADC as shown in Figure 5, taken from the Microchip documentation (section 17, figure 17-1).

#### Figure 5 – PIC32MX695F512L ADC architecture

Each of the eight analog voltages is connected through an analog multiplexer to one of the multiplexed ADC inputs of the PIC (AN2, AN3, AN4, & AN5). Thus, with four main FPGAs the PIC can sample 32 voltage/current/fault parameters from the main FPGAs by first selecting which PIC ADC input is to be used (which main FPGA), then asserting a 3-bit analog mux selection code (which analog value of the selected FPGA block), and then performing a conversion. Through the front panel Ethernet interface the PIC may be commanded at any time to scan all channels and save a block of conversions to local memory. These values may then be read out through that same Ethernet interface to monitor all useful voltages & currents.

#### **1.6.1** Temperature monitoring

The Virtex-6 FPGAs have temperature monitoring capability using the "System Monitor" block of the FPGA, as described in Xilinx document UG320. The AVDD pin of each Virtex-6 has been connected to the +2.5V power supply, and the AVSS, VREFP and VREFN pins are all tied to ground, setting up the "System Monitor" for its simplest configuration using the internal reference. The "System Monitor" temperature is regularly sampled and made available through the register interface of each FPGA build (Pipeline, ATCA Interface and SSB Emulator).

A secondary method of temperature measurement is supported by the PIC and the Management FPGA. This method uses the variable output voltage obtained from the Comparator Reference block of the PIC, and four digital outputs from the Management FPGA. Through these connections the temperature sensing diode of each main FPGA may be separately energized and the voltage dropped across the selected diode read using analog input channel AD11 of the PIC.

#### 1.6.2 Monitoring through ATCA

The LAPP IPMC is connected to the PIC via an I2C bus so that the PIC is the single "sensor" for the entire board. Interrupt-driven software within the PIC based upon a timer may perform measurements of all voltage, current and temperature parameters in the background, leaving the most recent measurements in a block of memory. When accessed by the LAPP IPMC, this block of memory may be read out and made available to the Shelf Manager.

## 2 ELECTRICAL & MECHANICAL SPECIFICATIONS

## 2.1 PC board construction

The FLIC is standard FR-4 construction with 18 trace layers. The surface finish is electroless gold over nickel (ENIG) with white silkscreen over liquid photo-imageable soldermask on both sides. All differential traces are 100 ohm characteristic impedance.

## 2.2 Mechanical specifics

The FLIC is the standard size specified in PICMG 3.0 for an ATCA front board. A Schroff front panel with Southco handles (ATCA standard) is used.

## 2.3 Power and Cooling requirements

Nominal power dissipation of the FLIC is 57 Watts with all FPGAs fully programmed and active. Of this, approximately 8 Watts is management power.

### 2.4 Front Panel Connectors

Front panel connections to the FLIC include two JTAG connectors, a PIC programming connector and a front panel Ethernet port.

#### 2.4.1 JTAG Connectors

Two JTAG connectors are provided at the front of the FLIC for debugging and analysis of FPGA operation. Due to the differing voltage requirements of the Spartan-3 vs. the Virtex-6, unique JTAG chains are required. Two standard 20-pin Xilinx JTAG connectors are provided, one for each chain, immediately behind the front panel, as shown in Figure 6. The Main FPGA JTAG chain uses +2.5V power as is required for Virtex-6 FPGAs. The Management FPGA JTAG chain uses +3.3V power as is required for the Spartan-3.

Figure 6 – JTAG connector location and identification

Internal zero ohm resistors are used to provide oscilloscope probing points for debugging of JTAG problems. These resistor sets, one per Virtex-6, may be installed in two different ways to either include or exclude the given FPGA from the JTAG chain.

#### 2.4.2 PIC programming connector

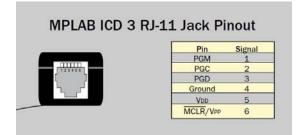

A 6-pin telephone (RJ-11) jack is used for the PIC programming interface. Figure 7 shows the pinout, taken from the Microchip web site at

http://ww1.microchip.com/downloads/en/DeviceDoc/DS-51765C.pdf.

Figure 7 – Microchip PIC ICD connector pinout

#### 2.4.3 Front Panel Ethernet connector

The front panel Ethernet connection of the FLIC is a standard RJ-45 connector (Amphenol J00-0065NL with internal magnetics). The FLIC uses a KSZ8051RNL PHY and supports communication at speeds up to 100BASE-T.

#### 2.4.4 Front Panel LED indicators

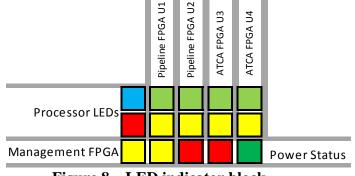

Twelve front panel LED indicators provide general status. The LEDs are arranged in a 5x3 block of LEDs with 7 subsections as shown in Figure 8.

The two Processor LEDs are labeled ATCA (blue) and ERR (red). If an IPMC module is plugged into the FLIC a resistor stuffing option allows the "ATCA" LED to be driven by the IPMC in accordance with ATCA specifications. In the default assembly the "ATCA" LED is driven by the on-board PIC processor and is used for generic status. The ERR indicator is normally illuminated when the FLIC has no Ethernet connection on the front panel port and extinguishes when an Ethernet connection is present.

The two Management FPGA LEDs are the CNFG (configure) and the PROG (labeled "P") indicators. Both LEDs are under the control of the Management FPGA and are generally used to indicate the status of firmware download to the four main FPGAs. However, these LEDs are under firmware control of the Management FPGA and the exact meaning depends upon the firmware version in place.

Three Power Status LEDs, labeled "A", "B" and "M", display the power state of the FLIC. The "A" LED is illuminated if the +3.3V management power to the FLIC is present and the internal voltage monitor for the Management FPGA indicates that all sub-voltages derived from management power are within tolerance. The "B" LED illuminates if the board-wide +3.3V power is enabled. The "M" LED illuminates if the +3.3V management power is present.

Each Virtex-6 main FPGA of the FLIC ("U1" through "U4") drives two LEDs. The upper green LED is labeled "EV" (for "event") for each and the lower yellow LED is labeled "FC" (for "flow control") as the nominal expected usage is to illuminate the LEDs to indicate that records are being processed and/or that flow control is being asserted. However, both LEDs are defined by the exact firmware loaded into the main FPGAs and thus the meaning of each may vary.

#### 2.4.5 IPMC module LED signals

The IPMC module from LAPP has four LED output signals named ATCA, LED1, LED2 and LED3, all of which are defined by whatever firmware is running within the processors of the IPMC module. As previously noted a resistor stuffing option allows the blue ATCA LED of the FLIC to be driven by the ATCA output of the IPMC. The LED1 and LED2 outputs of the IPMC are connected to input pins of the PIC microcontroller to allow either of these signals to be monitored or optionally routed out to the 2<sup>nd</sup> processor LED (ERR) by firmware if deemed necessary.

## 2.5 Rear Connectors

The FLIC conforms to all rear connector pinouts for ATCA Zone 1 and ATCA Zone 2 as specified in PICMG 3.0. Additional connectors in Zone 3 are used for the RTM of the FLIC, with a custom pinout as defined in Table 1**Error! Reference source not found.** Each pair of rows services one SFP of the RTM, as indicated by the bold lines.

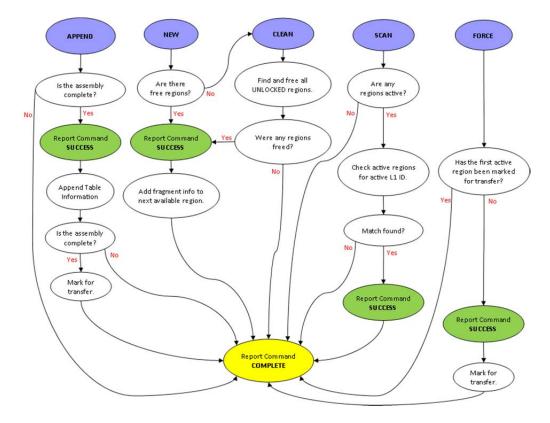

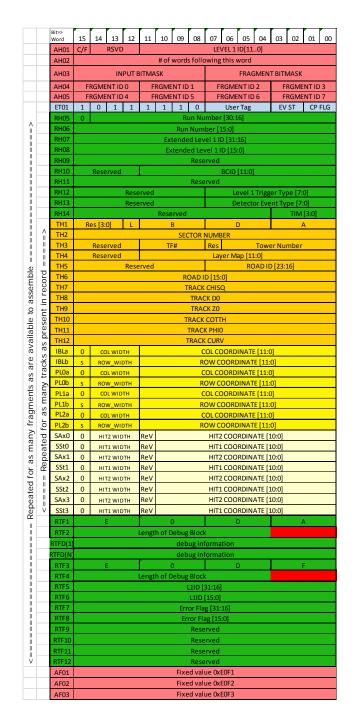

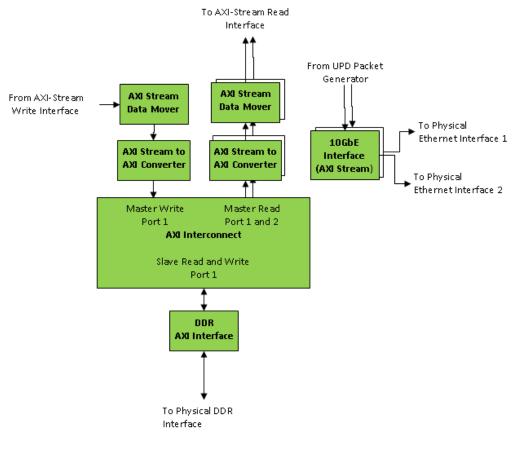

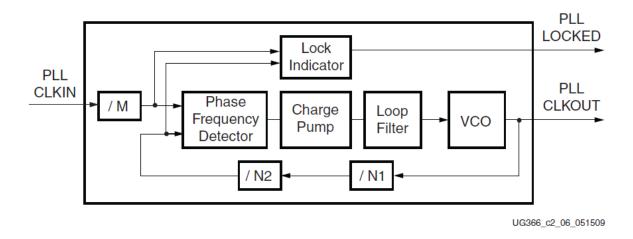

| Row   | Pin A | Pin B | Pin AB | Pin C | Pin D   | Pin CD | Pin E                    | Pin F | Pin EF | Pin G               | Pin H  | Pin GH |